# **Parallel Computing**

## Peter Bastian

email: peter.bastian@iwr.uni-heidelberg.de  $Olaf\ Ippisch$

$email: \verb|olaf.ippisch@iwr.uni-heidelberg.de|$

## November 9, 2009

## Contents

| 1 | Para | allel Computing                              | 3  |

|---|------|----------------------------------------------|----|

|   | 1.1  | Introduction                                 | 3  |

|   |      | 1.1.1 Why Parallel Computing?                | 3  |

|   |      | 1.1.2 (Very Short) History of Supercomputers | 4  |

|   | 1.2  | Single Processor Architecture                | 6  |

|   |      | 1.2.1 Von Neumann Architecture               | 6  |

|   |      | 1.2.2 Pipelining                             | 7  |

|   |      | 1.2.3 Superscalar Architecture               | 8  |

|   |      | 1.2.4 Caches                                 | 9  |

|   | 1.3  | Parallel Architectures                       | 12 |

|   |      | 1.3.1 Classifications                        | 12 |

|   |      | 1.3.2 Uniform Memory Access Architecture     | 13 |

|   |      | 1.3.3 Nonuniform Memory Access Architecture  | 14 |

|   |      | 1.3.4 Private Memory Architecture            | 17 |

|   | 1.4  | Things to Remember                           | 19 |

| 2 | Para | allel Programming                            | 20 |

|   | 2.1  | A Simple Notation for Parallel Programs      | 20 |

|   | 2.2  | First Parallel Programm                      | 20 |

|   | 2.3  | Mutual Exclusion                             | 22 |

|   | 2.4  | Single Program Multiple Data                 | 23 |

|   | 2.5  | Condition Synchronisation                    | 24 |

|   | 2.6  | Barriers                                     | 25 |

|   |      | 2.6.1 Things to Remember                     | 26 |

| 3 | Ope  | enMP                                         | 27 |

| 4 | Basi | ics of Parallel Algorithms                   | 32 |

|   | 4.1  | Data Decomposition                           | 33 |

|   | 4.2  | Agglomeration                                | 35 |

|    | 4.3   | Mapping of Processes to Processors         |

|----|-------|--------------------------------------------|

|    | 4.4   | Load Balancing                             |

|    | 4.5   | Data Decomposition of Vectors and Matrices |

|    | 4.6   | Matrix-Vector Multiplication               |

|    |       | 4.6.1 Things to Remember                   |

| 5  | Intro | oduction Message Passing                   |

|    | 5.1   | Synchronous Communication                  |

|    | 5.2   | Asynchronous Communication                 |

| 6  | Deb   | ugging of Parallel Programs                |

| 7  | The   | Message Passing Interface                  |

|    | 7.1   | Simple Example                             |

|    | 7.2   | Communicators and Topologies               |

|    | 7.3   | Blocking Communication                     |

|    | 7.4   | Non-blocking communication                 |

|    | 7.5   | Global Communication                       |

|    | 7.6   | Avoiding Deadlocks: Coloring               |

| 8  | Thin  | gs to Remember                             |

| 9  | Ana   | lysis of Parallel Algorithms               |

|    | 9.1   | Examples                                   |

|    |       | 9.1.1 Scalar Product                       |

|    |       | 9.1.2 Gaussian Elimination                 |

|    |       | 9.1.3 Grid Algorithm                       |

|    | 9.2   | Scalability                                |

|    |       | 9.2.1 Fixed Size                           |

|    |       | 9.2.2 Scaled Size                          |

|    | 9.3   | Things to Remember                         |

| 10 | Prog  | gramming with CUDA (                       |

|    | 10.1  | Introduction                               |

|    |       | Hardware Implementation                    |

|    |       | CUDA eyamples                              |

## 1 Parallel Computing

#### 1.1 Introduction

This set of lectures gives a basic introduction to the subject.

At the end you should have acquired:

- A basic understanding of different parallel computer architectures.

- Know how to write programs using OpenMP.

- Know how to write programs using message passing.

- Know how to write parallel programs using the CUDA environment.

- Know how to evaluate the quality of a parallel algorithm and its implementation.

## 1.1.1 Why Parallel Computing?

## **Parallel Computing is Ubiquitous**

- Multi-Tasking

- Several independent computations ("threads of control") can be run quasi-simultaneously on a single processor (time slicing).

- Developed since 1960s to increase throughput.

- Interactive applications require "to do many things in parallel".

- All relevant coordination problems are already present (That is why we can "simulate" parallel programming on a single PC".

- "Hyperthreading" does the simulation in hardware.

- Most processors today offer execution in parallel ("multi-core").

## • Distributed Computing

- Computation is inherently distributed because the information is distributed.

- Example: Running a world-wide company or a bank.

- Issues are: Communication across platforms, portability and security.

## • High-Performance Computing

- HPC is the driving force behind the development of computers.

- All techniques implemented in today's desktop machines have been developed in supercomputers many years ago.

- Applications run on supercomputers are mostly numerical simulations.

- Grand Challenges: Cosmology, protein folding, prediction of earth-quakes, climate and ocean flows, . . .

- but also: nuclear weapon simulation

- ASCI (Advanced Simulation and Computing) Program funding: \$ 300 million in 2004.

- Earth simulator (largest computer in the world from 2002 to 2004) cost about \$ 500 million.

## 1.1.2 (Very Short) History of Supercomputers

## What is a Supercomputer?

• A computer that costs more than \$ 10 million

| Computer      | Year | \$     | MHz  | MBytes           | MFLOP/s          |

|---------------|------|--------|------|------------------|------------------|

| CDC 6600      | 1964 | 7M \$  | 10   | 0.5              | 3.3              |

| Cray 1A       | 1976 | 8M \$  | 80   | 8                | 20               |

| Cray X-MP/48  | 1986 | 15M \$ | 118  | 64               | 220              |

| C90           | 1996 |        | 250  | 2048             | 5000             |

| ASCI Red      | 1997 |        | 220  | $1.2 \cdot 10^6$ | $2.4 \cdot 10^6$ |

| Pentium 4     | 2002 | 1500   | 2400 | 1000             | 4800             |

| Intel QX 9770 | 2008 | 1200   | 3200 | > 4000           | $10^{6}$         |

- Speed is measured in floating point operations per second (FLOP/s).

- Current supercomputers are large collections of microprocessors

- Today's desktop PC is yesterdays supercomputer.

- www.top500.org compiles list of supercomputers every six months.

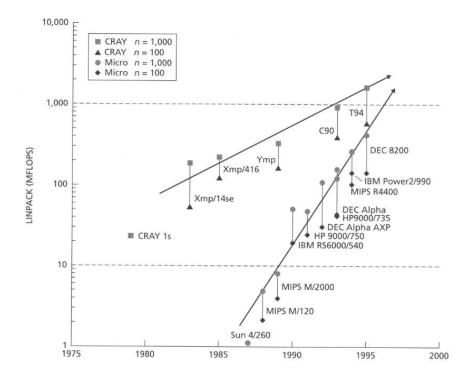

## **Development of Microprocessors**

Microprocessors outperform conventional supercomputers in the mid 90s (from *Culler et al.*).

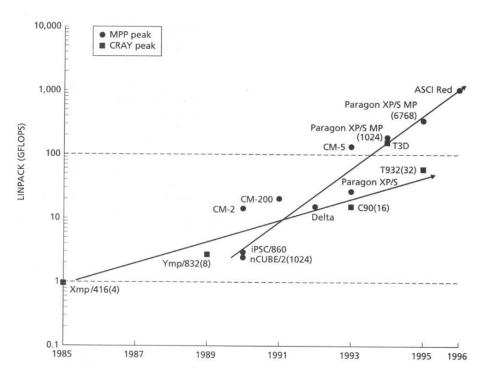

## **Development of Multiprocessors**

Massively parallel machines outperform vector parallel machines in the early 90s (from Culler et~al.).

TOP 500 November 2007

| Rank | Site                                                                                      | Computer/Year Vendor                                                                                                                                      | Cores  | R <sub>max</sub> | R <sub>peak</sub> | Power   |

|------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-------------------|---------|

| 1    | DOE/NNSA/LANL<br>United States                                                            | Roadrunner - BladeCenter QS22/LS21<br>Cluster, PowerXCell 8i 3.2 Ghz./<br>Opteron DC 1.8 GHz, Voltaire Infiniband<br>/2008<br>IBM                         | 129600 | 1105.00          | 1456.70           | 2483.47 |

| 2    | Oak Ridge National Laboratory<br>United States                                            | Jaguar - Cray XT5 QC 2.3 G Hz / 2008<br>Cray Inc.                                                                                                         | 150152 | 1059.00          | 1381.40           | 6950.60 |

| 3    | Forschungszentrum Juelich (FZJ)<br>Germany                                                | JUGENE - Blue Gene/P Solution / 2009<br>IBM                                                                                                               | 294912 | 825.50           | 1002.70           | 2268.00 |

| 4    | NASA/Ames Research Center/NAS<br>United States                                            | Pleiades - SGI Altix ICE 8 200EX, Xeon<br>OC 3 .0/2.66 G Hz / 2008<br>SGI                                                                                 | 51200  | 487.01           | 608.83            | 2090.00 |

| 5    | DOE/NNSA/LLNL<br>United States                                                            | BlueGene/L - e Server Blue Gene<br>Solution / 2007<br>IBM                                                                                                 | 212992 | 478.20           | 596.38            | 2329.60 |

| 6    | National Institute for Computational<br>Sciences/University of Tennessee<br>United States | Kraken XT5 - Cray XT5 QC 2.3 GHz./<br>2008<br>Cray Inc.                                                                                                   | 66000  | 463.30           | 607.20            |         |

| 7    | Argonne National Laboratory<br>United States                                              | Blue Gene/P Solution / 2007<br>IBM                                                                                                                        | 163840 | 458.61           | 557.06            | 1260.00 |

| 8    | Texas Advanced Computing<br>Center/Univ. of Texas<br>United States                        | Ranger - Sun Blade x6420, Opteron QC<br>2.3 Ghz., hfiniband / 2008<br>Sun Microsystems                                                                    | 62976  | 433.20           | 579.38            | 2000.00 |

| 9    | DOE/NNSA/LLNL<br>United States                                                            | Dawn - Blue Gene/P Solution / 2009<br>IBM                                                                                                                 | 147456 | 415.70           | 501.35            | 1134.00 |

| 10   | Forschungszentrum Juelich (FZJ)<br>Germany                                                | JUROPA - Sun Constellation ,<br>Nova Scale R422-E2, Intel Xeon X5570 ,<br>2.93 GHz, Sun MaMellanox ODR<br>Infiniband/Partec Parastation / 2009<br>Bull SA | 26304  | 274.80           | 308.28            | 1549.00 |

3. BlueGene/P "JUGENE" at FZ Jülich: 294912 processors(cores),  $825.5~\mathrm{TFLOP/s}$

## **Terascale Simulation Facility**

BlueGene/L prototype at Lawrence Livermore National Laboratory outperforms Earth Simulator in late 2004: 65536 processors, 136 TFLOP/s,

Final version at LLNL in 2006: 212992 processors, 478 TFLOP/s

## **Efficient Algorithms are Important!**

• Computation time for solving (certain) systems of linear equations on a computer with 1 GFLOP/s.

| $\overline{}$  | Gauss $(\frac{2}{3}N^3)$ | Multigrid $(100N)$  |

|----------------|--------------------------|---------------------|

| 1.000          | $0.66 \mathrm{\ s}$      | $10^{-4} { m s}$    |

| 10.000         | $660 \mathrm{\ s}$       | $10^{-3} \text{ s}$ |

| 100.000        | $7.6 \mathrm{d}$         | $10^{-2} \text{ s}$ |

| $1 \cdot 10^6$ | 21 y                     | $0.1 \mathrm{\ s}$  |

| $1 \cdot 10^7$ | 21.000 y                 | 1 s                 |

- Parallelisation does not help an inefficient algorithm.

- We must parallelise algorithms with good sequential complexity.

## 1.2 Single Processor Architecture

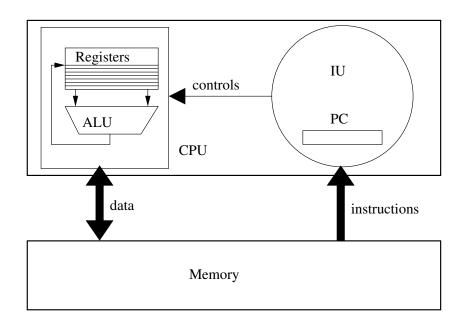

## 1.2.1 Von Neumann Architecture

Von Neumann Computer

## IU: Instruction unit

PC: Program counter

ALU: Arithmetic logic unit

CPU: Central processing unit

Single cycle architecture

## 1.2.2 Pipelining

## Pipelining: General Principle

|       | au    | $2\tau$ | $3\tau$ | $4\tau$ |       |       |

|-------|-------|---------|---------|---------|-------|-------|

| $T_1$ | $x_1$ | $x_2$   | $x_3$   | $x_4$   |       |       |

| $T_2$ |       | $x_1$   | $x_2$   | $x_3$   | $x_4$ |       |

| $T_3$ |       |         | $x_1$   | $x_2$   | $x_3$ | $x_4$ |

| $T_4$ |       |         |         | $x_1$   | $x_2$ | $x_3$ |

|       |       |         |         |         |       | time  |

- Task T can be subdivided into m subtasks  $T_1, \ldots, T_m$ .

- Every subtask can be processed in the same time  $\tau$ .

- All subtasks are **independent**.

$\bullet$  Time for processing N tasks:

$$T_S(N) = Nm\tau$$

$T_P(N) = (m+N-1)\tau$ .

• Speedup

$$S(N) = \frac{T_S(N)}{T_P(N)} = m \frac{N}{m+N-1}.$$

## **Arithmetic Pipelining**

- Apply pipelining principle to floating point operations.

- Especially suited for "vector operations" like  $s = x \cdot y$  or x = y + z because of independence property.

- Hence the name "vector processor".

- Allows at most  $m = 10 \dots 20$ .

- Vector processors typically have a very high memory bandwith.

- This is achieved with *interleaved* memory, which is pipelining applied to the memory subsystem.

## **Instruction Pipelining**

- Apply pipelining principle to the processing of machine instructions.

- Aim: Process one instruction per cycle.

- Typical subtasks are (m=5):

- Instruction fetch.

- Instruction decode.

- Instruction execute.

- Memory access.

- Write back results to register file.

- Reduced instruction set computer (RISC): Use simple and homogeneous set of instructions to enable pipelining (e. g. load/store architecture).

- Conditional jumps pose problems and require some effort such as branch prediction units.

- Optimising compilers are also essential (instruction reordering, loop unrolling, etc.).

## 1.2.3 Superscalar Architecture

#### **Superscalar Architecture**

• Consider the statements

- (1) a = b+c;

- (2) d = e\*f;

- (3) g = a-d;

- (4) h = i\*j;

- Statements 1, 2 and 4 can be executed in parallel because they are independent.

- This requires

- Ability to issue several instructions in one cycle.

- Multiple functional units.

- Out of order execution.

- Speculative execution.

- A processor executing more than one instruction per cycle is called superscalar.

- Multiple issue is possible through:

- A wide memory access reading two instructions.

- Very long instruction words.

- Multiple functional units with out of order execution were implemented in the CDC 6600 in 1964.

- A degree of parallelism of 3...5 can be achieved.

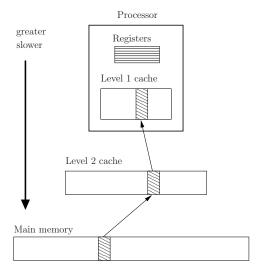

#### 1.2.4 Caches

#### Caches I

While the processing power increases with parallisation, the memory bandwidth usually does not

- Reading a 64-bit word from DRAM memory can cost up to 50 cycles.

- Building fast memory is possible but too expensive per bit for large memories.

- Hierarchical cache: Check if data is in the level *l* cache, if not ask the next higher level.

- Repeat until main memory is asked.

- Data is transferred in *cache lines* of 32 ... 128 bytes (4 to 16 words).

#### Caches II

- Caches rely on spatial and temporal locality.

- There are four issues to be discussed in cache design:

- Placement: Where does a block from main memory go in the cache? Direct mapped cache, associative cache.

- *Identification*: How to find out if a block is already in cache?

- Replacement: Which block is removed from a full cache?

- Write strategy: How is write access handled? Write-through and write-back caches.

- Caches require to make code cache-aware. This is usually non-trivial and not done automatically.

- Caches can lead to a slow-down if data is accessed randomly and not reused.

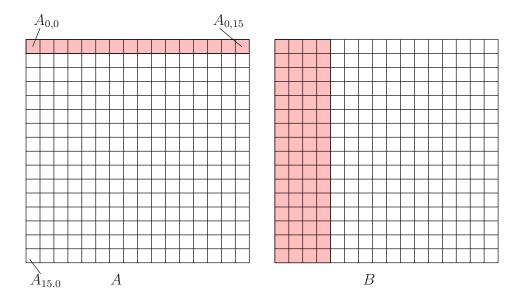

## Cache Use in Matrix Multiplication

- Compute product of two matrices C = AB, i.e.  $C_{ij} = \sum_{k=1}^{N} A_{ik} B_{kj}$

- Assume cache lines containing four numbers. C layout:

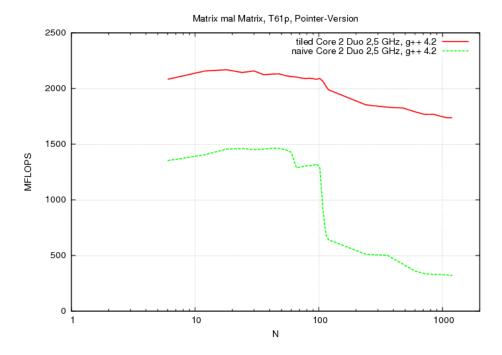

## **Matrix Multiplication Performance**

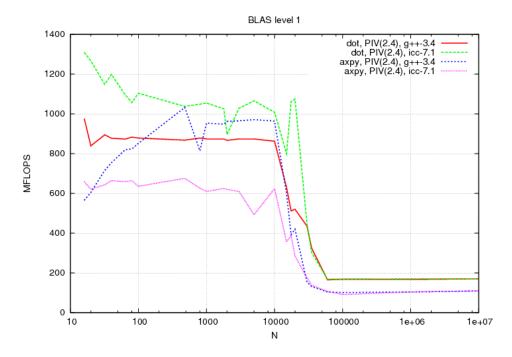

**BLAS1** Performance

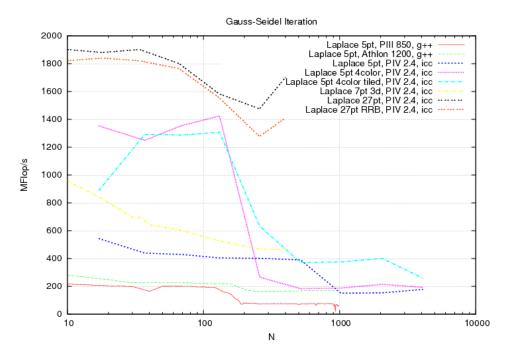

**Laplace Performance**

#### 1.3 Parallel Architectures

#### 1.3.1 Classifications

Flynn's Classification (1972)

|                       | Single data stream | Multiple data streams |

|-----------------------|--------------------|-----------------------|

|                       | (One ALU)          | (Several ALUs)        |

| Single instruction    | SISD               | SIMD                  |

| stream, (One IU)      |                    |                       |

| Multiple instruction  |                    | MIMD                  |

| streams (Several IUs) |                    |                       |

- **SIMD** machines allow the synchronous execution of one instruction on multiple ALUs. Important machines: ILLIAC IV, CM-2, MasPar. And now CUDA!

- MIMD is the leading concept since the early 90s. All current supercomputers are of this type.

## **Classification by Memory Access**

- ullet Flynn's classification does not state how the individual components exchange data.

- There are only two basic concepts.

- Communication via shared memory. This means that all processors share a global address space. These machines are also called multiprocessors.

- Communication via message exchange. In this model every processor has its own local address space. These machines are also called multicomputers.

## 1.3.2 Uniform Memory Access Architecture

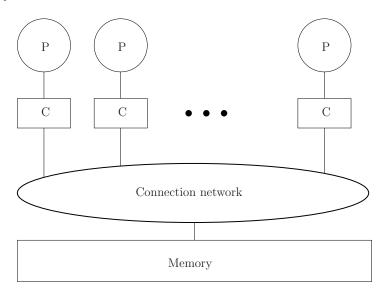

## **Uniform Memory Access Architecture**

- UMA: Access to every memory location from every processor takes the same amount of time.

- This is achieved through a *dynamic network*.

- Simplest "network": bus.

- Caches serve two reasons: Provide fast memory access (migration) and remove traffic from network (replication).

- Cache coherence problem: Suppose one memory block is in two or more caches and is written by a processor. What to do now?

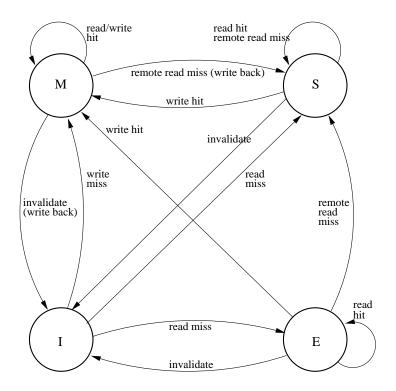

## **Bus Snooping, MESI-Protocol**

- Assume that network is a bus.

- All caches *listen* on the bus whether one of their blocks is affected.

- MESI-Protocol: Every block in a cache is in one of four states: Modified, exclusive, shared, invalid.

- Write-invalidate, write-back protocol.

- State transition diagram is given on the left.

- Used e.g. in the Pentium.

## 1.3.3 Nonuniform Memory Access Architecture

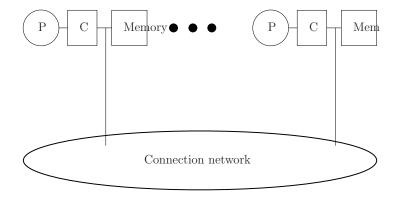

## **Nonuniform Memory Access Architecture**

• Memories are associated with processors but address space is global.

- Access to local memory is fast.

- Access to remote memories is via the network and slow.

- Including caches there are at least three different access times.

- Solving the cache-coherence problem requires expensive hardware (ccNUMA).

- Machines up to 1024 processors have been built.

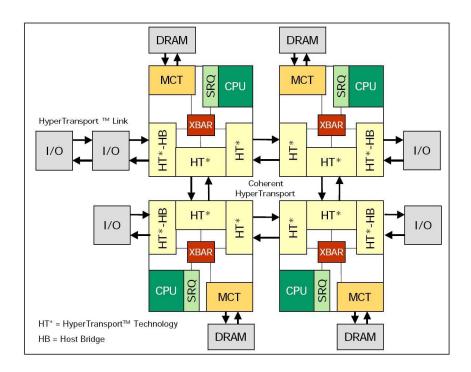

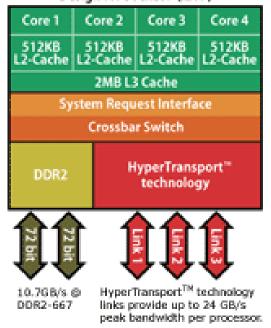

## AMD Hammer Architecture Generation 8, introduced 2001

Barcelona QuadCore, Generation 10h, 2007

Quad-Core AMD Opteron\*\* Processor Design for Socket F (1207)

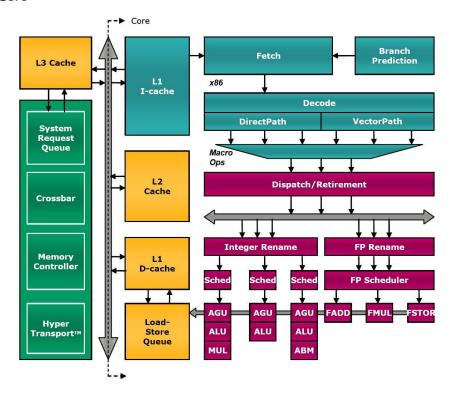

#### **Barcelona Core**

#### **Barcelona Details**

• L1 Cache

- 64K instructions, 64K data.

- Cache line 64 Bytes.

- 2 way associative, write-allocate, writeback, least-recently-used.

- MOESI (MESI extended by "owned").

#### • L2 Cache

- Victim cache: contains only blocks moved out of L1.

- Size implementation dependent.

#### • L3 Cache

- non-inclusive: data either in L1 or L3.

- Victim Cache for L2 blocks.

- Heuristics for determining blocks shared by some cores.

#### • Superscalarity

- Instruction decode, Integer units, FP units, address generation 3-fold (3 OPS per cycle).

- Out of order execution, branch prediction.

- Pipelining: 12 stages integer, 17 stages floating-point (Hammer).

- Integrated memory controller, 128 bit wide.

- HyperTransport: coherent access to remote memory.

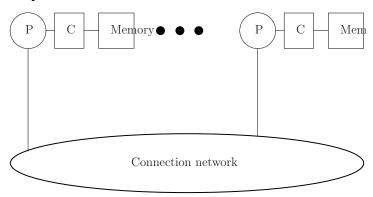

#### 1.3.4 Private Memory Architecture

- Processors can only access their local memory.

- Processors, caches and main memory are standard components: Cheap, Moore's law can be fully utilised.

- Network can be anything from fast ethernet to specialised networks.

- $\bullet$  Most scalable architecture. Current supercomputers already have more than  $10^5$  processors.

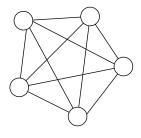

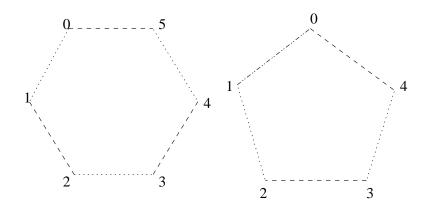

## **Network Topologies**

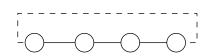

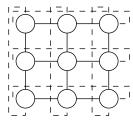

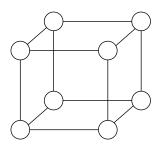

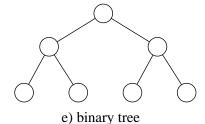

b) 1D-array, ring

a) fully connected

c) 2D-array, 2D-torus

d) Hypercube, 3D-array

- There are many different types of topologies used for packet-switched networks.

- 1-,2-,3-D arrays and tori.

- Fully connected graph.

- Binary tree.

- Hypercube: HC of dimension  $d \ge 0$  has  $2^d$  nodes. Nodes x, y are connected if their bit-wise representations differs in one bit.

- k-dimensional arrays can be embedded in hypercubes.

- Topologies are useful in algorithms as well.

## Comparison of Architectures by Example

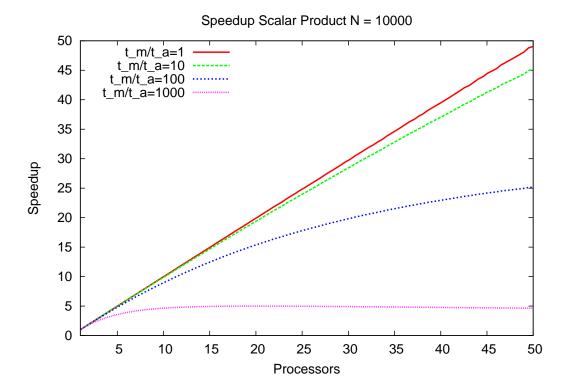

- Given vectors  $x, y \in \mathbb{R}^N$ , compute scalar product  $s = \sum_{i=0}^{N-1} x_i y_i$ :

- (1) Subdivide index set into P pieces.

- (2) Compute  $s_p = \sum_{i=pN/P}^{(p+1)N/P-1} x_i y_i$  in parallel.

- (3) Compute  $s = \sum_{i=0}^{P-1} s_i$ . This is treated later.

- Uniform memory access architecture: Store vectors as in sequential program:

• Nonuniform memory access architecture: Distribute data to the local memories:

- Message passing architecture: Same as for NUMA!

- Distributing data structures is hard and not automatic in general.

- Parallelisation effort for NUMA and MP is almost the same.

## 1.4 Things to Remember

#### What you should remember

- Modern microprocessors combine all the features of yesterdays supercomputers.

- Today parallel machines have arrived on the desktop.

- MIMD is the dominant design.

- There are UMA, NUMA and MP architectures.

- Only machines with local memory are scalable.

- Algorithms have to be designed carefully with respect to the memory hierarchy.

#### References

- [1] ASC (former ASCI) program website. http://www.sandia.gov/NNSA/ASC/

- [2] Achievements of Seymour Cray. http://research.microsoft.com/users/gbell/craytalk/

- [3] TOP 500 Supercomputer Sites. http://www.top500.org/

- [4] D. E. Culler, J. P. Singh and A. Gupta (1999). Parallel Computer Architecture. Morgan Kaufmann.

## 2 Parallel Programming

## 2.1 A Simple Notation for Parallel Programs

#### **Communicating Sequential Processes**

#### Sequential Program

Sequence of statements. Statements are processed one after another.

#### (Sequential) Process

A sequential program in execution. The state of a process consists of the values of all variables and the next statement to be executed.

## **Parallel Computation**

A set of interacting sequential processes. Processes can be executed on a single processor (time slicing) or on a separate processor each.

## Parallel Program

Specifies a parallel computation.

## A Simple Parallel Language

- First all global variables are initialized, then processes are started.

- Computation ends when all processes terminated.

- Processes share global address space (also called threads).

## 2.2 First Parallel Programm

#### **Example: Scalar Product with Two Processes**

- We neglect input/output of the vectors.

- Local variables are private to each process.

- Decomposition of the computation is on the **for**-loop.

```

\begin{array}{lll} \mathbf{parallel} \ \mathbf{two}\text{-}\mathbf{process}\text{-}\mathbf{scalar}\text{-}\mathbf{product} \ \{ & \mathbf{const} \ \mathbf{int} \ N=8; & // \ problem \ size \\ \mathbf{double} \ x[N], \ y[N], \ s=0; & // \ vectors, \ result \\ \mathbf{process} \ \Pi_1 & \{ & \mathbf{int} \ i; \ \mathbf{double} \ ss=0; \\ \mathbf{for} \ (i=0; \ i < N/2; \ i++) \ ss \ += \ x[i]^*y[i]; \\ s=s+ss; & // \ danger! \\ \} & \mathbf{process} \ \Pi_2 & \{ & \mathbf{int} \ i; \ \mathbf{double} \ ss=0; \\ \mathbf{for} \ (i=N/2; \ i < N; \ i++) \ ss \ += \ x[i]^*y[i]; \\ s=s+ss; & // \ danger! \\ \} & \} \end{array}

```

#### **Critical Section**

• Statement s=s+ss is not atomic:

- The order of execution of statements of different processes relative to each other is not specified

- This results in an exponentially growing number of possible orders of execution.

#### **Possible Execution Orders**

Only some orders yield the correct result!

#### **First Obervations**

- Work has to be distributed to processes

- Often Synchronisation of processes necessary

#### 2.3 Mutual Exclusion

#### **Mutual Exclusion**

- Additional *synchronisation* is needed to exclude possible execution orders that do not give the correct result.

- Critical sections have to be processed under mutual exclusion.

- Mutual exclusion requires:

- At most one process enters a critical section.

- No deadlocks.

- No process waits for a free critical section.

- If a process wants to enter, it will finally succeed.

- By [s = s + ss] we denote that all statements between "[" and "]" are executed only by one process at a time. If two processes attempt to execute "[" at the same time, one of them is delayed.

#### Machine Instructions for Mutual Exclusion

- In practice mutual exclusion is implemented with special machine instructions to avoid problems with consistency and performance.

- Atomic-swap: Exchange contents of a register and a memory location atomically.

- Test-and-set: Check if contents of a memory location is 0, if yes, set it to 1 atomically.

- Fetch-and-increment: Load memory location to register and increment the contents of the memory location by one atomically.

- Load-locked/store-conditional: Load-locked loads a memory location to a register, store-conditional writes a register to a memory location only if this memory location has not been written since the preceding load-locked. This requires interaction with the cache hardware.

- The first three operations consist of an atomic read-modify-write.

- The last one is more flexible and suited for load/store architectures.

## **Improved Spin Lock**

• Idea: Use atomic - swap only if it has been found true:

• Getting P processors through the lock requires  $O(P^2)$  time.

## 2.4 Single Program Multiple Data

#### **Parametrisation of Processes**

• We want to write programs for a variable number of processes:

```

parallel many-process-scalar-product {

const int N;

// problem size

const int P;

// number of processors

// vectors

double x[N], y[N];

// result

double s = 0;

process \Pi [int p \in \{0, ..., P-1\}]

int i; double ss = 0;

for (i = N * p/P; i < N * (p+1)/P; i++)

ss += x[i]*y[i];

[s=s+ss];

// sequential execution

}

}

```

• Single Program Multiple Data: Every process has the same code but works on different data depending on p.

### Scalar Product on NUMA Architecture

- Every process stores part of the vector as local variables.

- Indices are renumbered from 0 in each process.

```

\begin{array}{l} \textbf{parallel} \ \text{local-data-scalar-product} \ \{ \\ \textbf{const} \ \textbf{int} \ P, N; \\ \textbf{double} \ s = 0; \\ \\ \textbf{process} \ \Pi \ [ \ \textbf{int} \ p \in \{0, \dots, P-1\}] \\ \{ \\ \textbf{double} \ x[N/P+1], \ y[N/P+1]; \\ // \ \text{local part of the vectors} \\ \textbf{int} \ i; \ \textbf{double} \ ss = 0; \\ \\ \textbf{for} \ (i = 0, i < (p+1) * N/P - p * N/P; i + +) \ ss = ss + x[i] * y[i]; \\ [s = s + ss;] \\ \} \\ \} \end{array}

```

## 2.5 Condition Synchronisation

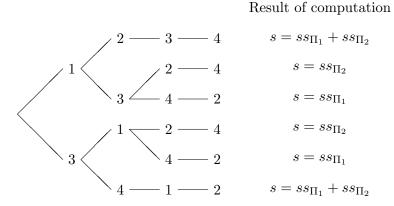

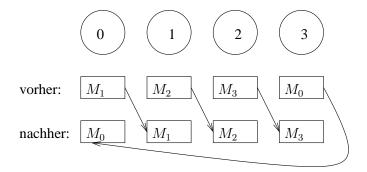

#### Parallelisation of the Sum

- Computation of the global sum of the local scalar products with [s = s + ss] is not parallel.

- It can be done in parallel as follows (P = 8):

$$s = \underbrace{s_0 + s_1}_{s_{01}} + \underbrace{s_2 + s_3}_{s_{23}} + \underbrace{s_4 + s_5}_{s_{45}} + \underbrace{s_6 + s_7}_{s_{67}}$$

• This reduces the execution time from O(P) to  $O(\log_2 P)$ .

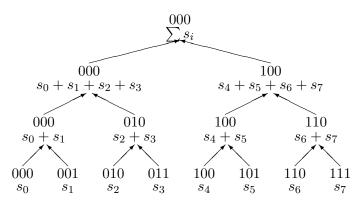

#### **Tree Combine**

Using a binary representation of process numbers, the communication structure forms a binary tree:

## Implementation of Tree Combine

```

parallel parallel-sum-scalar-product {

const int N = 100;

// problem size

const int d = 4, P = 2^d;

// number of processes

double x[N], y[N];

// vectors

double s[P] = \{0[P]\};

// results are global now

int flag[P] = \{0[P]\};

// flags, must be initialized!

process \Pi [int p \in \{0, ..., P-1\}] {

int i, m, k;

for (i = 0; i < d; i++) {

// bit i is 1

m=2^i;

if (p\&m) {flag[m]=1; break;} // I am ready

while (!flag[p|m]);

// condition synchronisation

s[p] = s[p] + s[p|m];

}

}

```

#### **Condition Synchronisation**

- A process waits for a condition (boolean expression) to become true. The condition is made true by another process.

- Here some processes wait for the flags to become true.

- Correct initialization of the flag variables is important.

- We implemented this synchronisation using busy wait.

- This might not be a good idea in multiprocessing.

- $\bullet$  The flags are also called  $condition\ variables.$

- When condition variables are used repeatedly (e.g. when computing several sums in a row) the following rules should be obeyed:

- A process that waits on a condition variable also resets it.

- A condition variable may only be set to true again if it is sure that it has been reset before.

#### 2.6 Barriers

#### **Barriers**

- At a barrier a process stops until all processes have reached the barrier.

- This is necessary, if e.g. all processes need the result of a parallel computation to go on.

- Sometimes it is called global synchronisation.

- A barrier is typically executed repeatedly as in the following code fragment:

```

while (1) {

compute something;

Barrier();

}

```

#### **Barrier for Two Processes**

• First we consider two processes  $\Pi_i$  and  $\Pi_j$  only:

```

\begin{array}{ll} \Pi_i \colon & \Pi_j \colon \\ \textbf{while } (\textit{arrived}[i]) \ ; & \textbf{while } (\textit{arrived}[j]) \ ; \\ \textit{arrived}[i] = 1; & \textit{arrived}[j] = 1; \\ \textbf{while } (\neg \textit{arrived}[j]) \ ; & \textbf{while } (\neg \textit{arrived}[i]) \ ; \\ \textit{arrived}[j] = 0; & \textit{arrived}[i] = 0; \end{array}

```

- arrived[i] that is true if process  $\Pi_i$  has arrived.

- Line 3 is the actual busy wait for the other process.

- A process immediately resets the flag it has waited for (lines 2,4).

- Lines 1,2 ensure that the flag has been reset before a process waits on it.

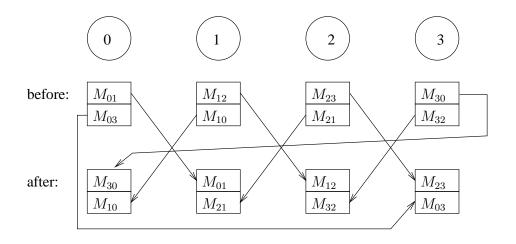

#### Barrier with Recursive Doubling II

```

{\bf parallel} \ {\bf recursive-doubling-barrier} \ \{

const int d = 4; const int P = 2^d;

int arrived[d][P] = \{0[P \cdot d]\};

// flag variables

process \Pi [int p \in \{0, ..., P-1\}] {

int i, q;

while (1) {

Computation;

for (i = 0; i < d; i++) {

// all stages

q = p \oplus 2^i;

// flip bit i

while (arrived[i][p]);

arrived[i][p]=1;

while (\neg arrived[i][q]);

arrived[i][q]=0;

}

}

}

}

```

## 2.6.1 Things to Remember

## What you should remember

• A parallel computation consists of a set of interacting sequential processes.

- Apart from the distribution of the work the synchronisation of the processes is also important

- Typical synchronisation mechanisms are: Mutual exclusion, condition synchronisation and barriers.

## 3 OpenMP

- OpenMP is a special implementation of multithreading

- current version 3.0 released in May 2008

- $\bullet$  available for Fortran and C/C++

- works for different operating systems (e.g. Linux, Windows, Solaris)

- integrated in various compilers (e.g. Intel icc > 8.0, gcc > 4.2, Visual Studio >= 2005, Sun Studio, . . . )

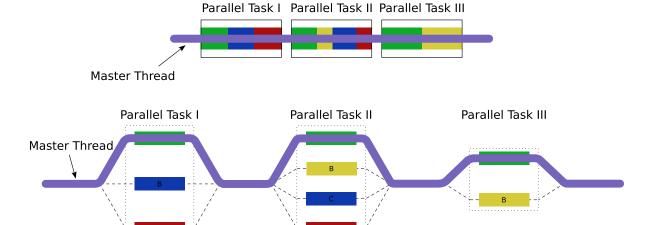

## Thread Model of OpenMP

figure from Wikipedia: "OpenMP"

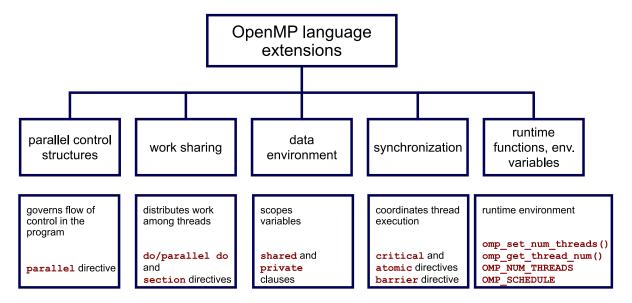

## OpenMP directives

OpenMP directives

- are an extension of the language

- are created by writting special pre-processor commands into the source code, which are interpreted by a suitable compiler

- start with \#pragma omp followed by a keyword and optionally some arguments

## **OpenMP Constructs**

figure from Wikipedia: "OpenMP"

## Scalar Product with OpenMP

```

#ifdef _OPENMP

2 #include < omp.h>

#endif

double ScalarProduct(std::vector < double > a,

std::vector<double> b)

6

{

const int N=a.size();

int i;

double sum = 0.0;

10

#pragma omp parallel for

for (i=0;i<N;++i)</pre>

12

sum += a[i] * b[i];

return(sum);

14

}

```

## Thread Initialisation

parallel starts a block which is run in parallel

sections inside a sections block there are several independent section blocks which can be executed independently.

if if an if is introduced in the thread initialisation command, the block is only executed in parallel if the condition after if is true.

#### **Synchronisation**

**critical** mutual exclusion: the block is only executed by one thread at a time.

atomic same as critical but tries to use hardware instructions

**single** the part inside the **single** block is only executed by one thread. The other threads are waiting at the end of the block.

master the part inside the master block is only executed by the master thread. It is skipped by all other threads.

barrier each thread waits till all threads have reached the barrier

**nowait** usually threads wait at the end of a block. If nowait is used they continue immediately

#### **Accessibility of Variables**

**shared** All threads are accessing the same (shared) data.

private Each thread has its own copy of the data.

**default** is used to specify what's the default behaviour for variables. Can be **shared**, **private** or **none**.

reduction If reduction(operator, variable) is specified, each thread uses a local copy of

variable but all local copies are combined with the operator operator at the end.

Possible operators are + \* - / & ^ |

#### **Scheduling of Parallel For-Loops**

The distribution of the total number of iterations to the individual threads can be influenced by the argument schedule of the pragma for. schedule is followed in brackets by one of five parameters and optionally after a comma the chunk size. The chunk size has to be an integer value known at compile time. The default schedule is implementation dependent.

**static** chunks are distributed at the beginning of the loop to the different threads.

**dynamic** each time a thread finishes its chunk it gets a new chunk.

**guided** the chunk size is proportional to the number of unassigned iterations divided by the number threads (i.e. chunk size is getting smaller with time).

**runtime** scheduling is controlled by the runtime variable OMP\_SCHEDULE. It is illegal to specify a chunk size.

**auto** scheduling is done by the compiler and/or runtime environment.

```

#define CHUNK_SIZE 10

2 #pragma omp parallel for schedule(dynamic, CHUNK_SIZE)

```

## Better Scalar Product with OpenMP

```

#ifdef _OPENMP

2 #include < omp.h>

#endif

double ScalarProduct(std::vector<double> a,

std::vector<double> b)

6

const int N=a.size();

int i;

double sum = 0.0, temp;

#pragma omp parallel for shared(a,b,sum) private(temp)

for (i=0; i<N; ++i)

12

temp = a[i] * b[i];

#pragma omp atomic

sum += temp;

return(sum);

```

## Improved Scalar Product with OpenMP

## **Parallel Execution of different Functions**

```

#pragma omp parallel sections

{

#pragma omp section

{

A();

B();

}

#pragma omp section

{

C();

D();

}

```

```

}

13  #pragma omp section

{

15    E();

F();

17  }

}

```

#### **Special OpenMP Functions**

There is a number of special functions which are defined in omp.h, e.g.

- int omp\_get\_num\_procs(); returns number of available processors

- int omp\_get\_num\_threads(); returns number of started threads

- int omp\_get\_thread\_num(); returns number of this thread

- void omp\_set\_num\_threads(int i); set the number of threads to be used

```

#ifdef _OPENMP

2 #ifdef _OPENMP

#include < omp.h>

4 #endif

#include <iostream >

6 const int CHUNK_SIZE=3;

8 int main(void)

{

10

int id:

std::cout << "Thisucomputeruhasu" << omp_get_num_procs() << "uprocessors" <<

std::endl;

\mathtt{std} :: \mathtt{cout} \; \mathrel{<<} \; \texttt{"Allowing} \; \mathsf{\_two} \; \mathsf{\_threads} \; \mathsf{\_per} \; \mathsf{\_processor} \; \mathrel{<<} \; \mathtt{std} :: \mathtt{endl} \; ;

12

omp_set_num_threads(2*omp_get_num_procs());

14

#pragma omp parallel default(shared) private(id)

16

#pragma omp for schedule(static,CHUNK_SIZE)

for (int i = 0; i < 7; ++i)

id = omp_get_thread_num();

20

std::cout << "HellowWorldwfromwthread" << id << std::endl;

22

#pragma omp master

24

std::cout << "Thereuareu" << omp_get_num_threads() << "uthreads" << std::endl;

return 0;

```

## Output

```

1 This computer has 2 processors

Allowing two threads per processor

3 Hello World from thread 1

Hello World from thread Hello World from thread 0

5 Hello World from thread 0

Hello World from thread 0

7 2Hello World from thread

```

```

1

9 Hello World from thread 1

There are 4 threads

11 There are 1 threads

```

#### **Compiling and Environment Variables**

OpenMP is activated with special compiler options. If they are not used, the #pragma statements are ignored and a sequential program is created. For icc the option is -openmp, for gcc it is -fopenmp

The environment variable OMP\_NUM\_THREADS specifies the maximal number of threads. The call of the function omp\_set\_num\_threads in the program has precedence over the environment variable

Example (with gcc and bash under linux):

```

gcc -02 -fopenmp -o scalar_product scalarproduct.cc

2 export OMP_NUM_THREADS=3

./scalar_product

```

#### References

- [1] OpenMP Specification http://openmp.org/wp/openmp-specifications/

- [2] OpenMP Tutorial in four parts http://www.embedded.com/design/multicore/201803777 (this is part four with links to part one to three)

- [3] Very complete OpenMP Tutorial/Reference https://computing.llnl.gov/tutorials/openMP

- [4] Intel Compiler (free for non-commercial use) http://www.intel.com/cd/software/products/asmona/eng/340679.htm

## 4 Basics of Parallel Algorithms

#### **Basic Approach to Parallelisation**

We want to have a look at three steps of the design of a parallel algorithm:

**Decomposition** of the problem into independent subtasks to identify maximal possible parallelism.

**Control of Granularity** to balance the expense for computation and communication.

**Mapping of Processes to Processors** to get an optimal adjustment of logical communication structure and hardware.

## 4.1 Data Decomposition

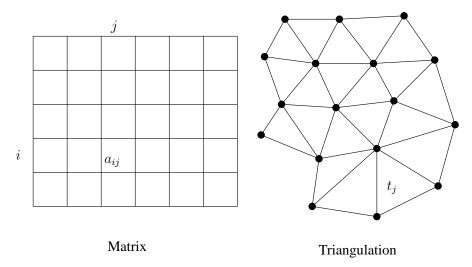

Algorithms are often tied to a special data structure. Certain operations have to be done for each data object.

Example: Matrix addition C = A + B, Triangulation

#### **Data Interdependence**

Often the operations for all data objects can't be done simultaneously.

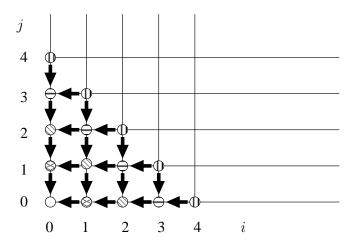

Example: Gauß-Seidel/SOR-Iteration with lexicographic numbering.

Calculations are done on a grid, where the calculation at grid point (i, j) depends on the gridpoints (i-1, j) and (i, j-1). Grid point (0, 0) can be calculated without prerequisites. Only grid points on the diagonal i + j = const can be calculated simultaneously.

Data interdependence complicates the data decomposition considerably.

## Increasing possible Parallelism

Sometimes the algorithm can be modified to allow for a higher data Independence.

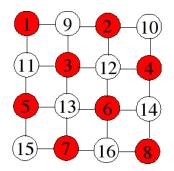

With a different numbering of the unknowns the possible degree of parallelism for the Gauß-Seidel/SOR-iteration scheme can be increased:

Every point in the domain gets a colour such that two neighbours never have the same colour. For structured grids two colours are enough (usually red and black are used). The unknowns of the same colour are numbered first, then the next colour ....

## **Red-Black-Ordering**

The equations for all unknowns with the same colour are then independent of each other. For structured grids we get a matrix of the form

$$A = \left(\begin{array}{cc} D_R & F \\ E & D_B \end{array}\right)$$

However, while such a matrix transformation does not affect the convergence of solvers like Steepest-Descent or CG (as they only depend on the matrix condition) it can affect the convergence rate of relaxation methods.

| $\overline{}$ |                            |                  |                            |                  |                            |                  |               | _ |                            |                  |                            |                            |                            |                  | _                |

|---------------|----------------------------|------------------|----------------------------|------------------|----------------------------|------------------|---------------|---|----------------------------|------------------|----------------------------|----------------------------|----------------------------|------------------|------------------|

| x             |                            |                  |                            |                  |                            |                  |               | x |                            | $\boldsymbol{x}$ |                            |                            |                            | F                |                  |

|               | $\boldsymbol{\mathcal{X}}$ |                  |                            |                  |                            |                  |               | х | $\boldsymbol{\mathcal{X}}$ |                  | $\boldsymbol{\mathcal{X}}$ |                            |                            | ·                |                  |

| -             |                            | $\chi$           |                            |                  |                            |                  |               | х |                            | $\chi$           | $\cdot x$                  | $\boldsymbol{\mathcal{X}}$ |                            |                  | -                |

|               |                            |                  | $\boldsymbol{\mathcal{X}}$ |                  |                            |                  |               |   | $\chi$                     |                  | $\chi$                     |                            | $\boldsymbol{\mathcal{X}}$ |                  |                  |

|               |                            |                  |                            | $\boldsymbol{x}$ |                            |                  |               |   |                            | $\boldsymbol{x}$ |                            | X                          |                            | $\boldsymbol{x}$ | -                |

| _             |                            |                  |                            |                  | $\boldsymbol{\mathcal{X}}$ |                  |               |   |                            |                  | $\boldsymbol{x}$           | $\boldsymbol{x}$           | $\boldsymbol{x}$           |                  | $\boldsymbol{x}$ |

| D             | R                          |                  |                            |                  |                            | $\boldsymbol{x}$ |               |   |                            |                  |                            | x                          |                            | x                | x                |

|               |                            |                  |                            |                  |                            |                  | $\mathcal{X}$ |   |                            |                  |                            |                            | $\boldsymbol{x}$           |                  | x                |

| х             | х                          | х                |                            |                  |                            |                  |               | х |                            |                  |                            |                            |                            |                  |                  |

| -             | x                          |                  | X                          |                  |                            |                  |               | - | X                          |                  |                            |                            |                            | $D_{B}$          | -                |

| x             |                            | $\boldsymbol{x}$ |                            | $\boldsymbol{x}$ |                            |                  |               |   |                            | $\boldsymbol{x}$ |                            |                            |                            |                  |                  |

|               | x                          | $\boldsymbol{x}$ | X                          |                  |                            |                  |               |   |                            |                  | $\boldsymbol{\mathcal{X}}$ |                            |                            |                  | -                |

|               |                            | $\boldsymbol{x}$ |                            | $\boldsymbol{x}$ | $\boldsymbol{x}$           | $\boldsymbol{x}$ |               |   |                            |                  |                            | x                          |                            |                  |                  |

|               |                            |                  | x                          |                  | $\boldsymbol{x}$           |                  | X             |   |                            |                  |                            |                            | x                          |                  |                  |

|               |                            |                  |                            | x                |                            | $\boldsymbol{x}$ |               |   |                            |                  |                            |                            |                            | $\boldsymbol{x}$ |                  |

| E             |                            |                  |                            |                  | $\boldsymbol{x}$           | $\boldsymbol{x}$ | X             |   |                            |                  |                            |                            |                            |                  | x                |

#### **Functional Decomposition**

Functional decomposition can be done, if different operations have to be done on the same data set.

Example: Compiler

A compiler consists of

- lexical analysis

- parser

- code generation

- optimisation

- assembling

Each of these steps can be assigned to a separate process. The data can run through this steps in portions. This is also called "Macro pipelining".

## Irregular Problems

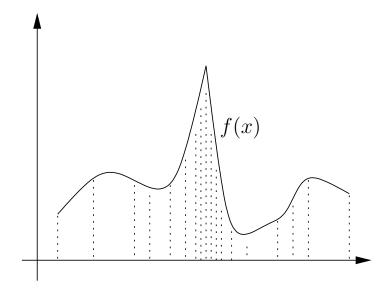

For some problems the decomposition cannot be determined a priory.

Example: Adaptive Quadrature of a function f(x)

The choice of the intervals depends on the function f and results from an evaluation of error predictors during the calculation.

## 4.2 Agglomeration

## **Agglomeration and Granularity**

The decomposition yields the maximal degree of parallelism, but it does not always make sense to really use this (e.g. one data object for each process) as the communication overhead can get too large.

Several subtasks are therefore assigned to each process and the communication necessary for each subtask is combined in as few messages as possible. This is called "agglomeration". This reduces the number of messages.

The granularity of a parallel algorithm is given by the ratio

$$\label{eq:granularity} \operatorname{granularity} = \frac{\operatorname{number of messages}}{\operatorname{computation time}}$$

Agglomeration reduces the granularity.

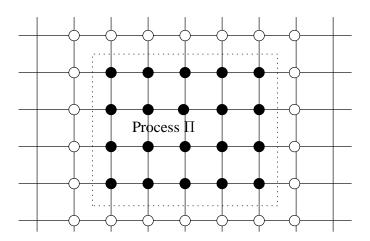

#### **Example: Gridbased Calculations**

Each process is assigned a number of grid points. In *iterative* calculations usually the value at each node and it's neighbours is needed. If there is no interdependence all calculations can be done in parallel. A process with N grid points has to do O(N) operations. With the partition it only needs to communicate  $4\sqrt{N}$  boundary nodes. The ratio of communication to computation costs is therefore  $O(N^{-1/2})$  and can be made arbitrarily small by increasing N. This is called *surface-to-volume-effect*.

#### 4.3 Mapping of Processes to Processors

#### **Optimal Mapping of Processes to Processors**

The set of all process  $\Pi$  forms a undirected graph  $G_{\Pi} = (\Pi, K)$ . Two processes are connected if they communicate.

The set of processors P together with the communication network (e.g. hypercube, field, ...) also forms a graph  $G_P = (P, N)$ .

If we assume  $|\Pi| = |P|$ , we have to choose which process is executed on which processor. In general we want to find a mapping, such that processes which communicate are mapped to proximate processors. This optimisation problem is a variant of the *graph partitioning problem* and is unfortunately  $\mathcal{NP}$ -complete.

As the transmission time in cut-through networks of state-of-the-art parallel computers is nearly independent of the distance, the problem of optimal process to processor mapping has lost a bit of it's importance. If many processes have to communicate simultaneously (which is often the case!), a good positioning of processes is still relevant.

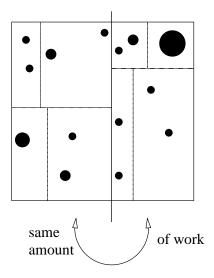

#### 4.4 Load Balancing

Load Balancing: Static Distribution

**Bin Packing** At beginning all processors are empty. Nodes are successively packed to the processor with the least work. This also works dynamically.

**Recursive Bisection** We make the additional assumption, that the nodes have a position in space. The domain is split into parts with an equal amount of work. This is repeated recursively on the subspaces.

## 4.5 Data Decomposition of Vectors and Matrices

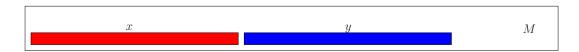

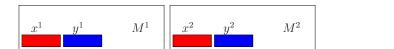

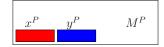

# **Decomposition of Vectors**

A vector  $x \in \mathbb{R}^N$  is a ordered list of numbers where each index  $i \in I = \{0, \dots, N-1\}$  is associated with a real number  $x_i$ .

Data decomposition is equivalent with a segmentation of the index set i in

$$I = \bigcup_{p \in P} I_p, \text{ with } p \neq q \Rightarrow I_p \cap I_q = \emptyset,$$

where P denotes the set of processes. For a good load balancing the subsets  $I_p$ ,  $p \in P$  should contain equal amounts of elements.

To get a coherent index set  $\tilde{I}_p = \{0, \dots, |I_p| - 1\}$  we define the mappings

$$\begin{array}{ll} p\colon & I\to P \text{ and}\\ \mu\colon & I\to \mathbb{N} \end{array}$$

which reversibly associate each index  $i \in I$  with a process  $p(i) \in P$  and a local index  $\mu(i) \in \tilde{I}_{p(i)}$ :  $I \ni i \mapsto (p(i), \mu(i))$ .

The inverse mapping  $\mu^{-1}(p,i)$  provides a global index to each local index  $i \in \tilde{I}_p$  and process  $p \in P$  i.e.  $p(\mu^{-1}(p,i)) = p$  and  $\mu(\mu^{-1}(p,i)) = i$ .

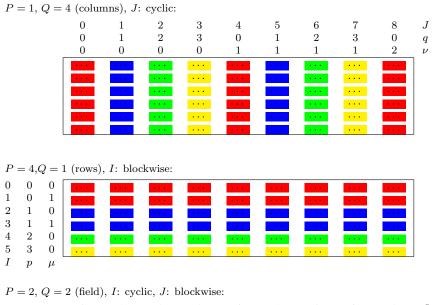

### **Common Decompositions: Cyclic**

$$p(i) = i\% P$$

$$\mu(i) = i \div P$$

$\div$  denotes an integer division and % the modulo function.

### Common Decompositions: Blockwise

$$p(i) = \begin{cases} i \div (B+1) & \text{if } i < R(B+1) \\ R + (i - R(B+1)) \div B & \text{else} \end{cases}$$

$$\mu(i) = \begin{cases} i\%(B+1) & \text{if } i < R(B+1) \\ (i - R(B+1))\%B & \text{else} \end{cases}$$

with

$$B = N \div P$$

and  $R = N \% P$

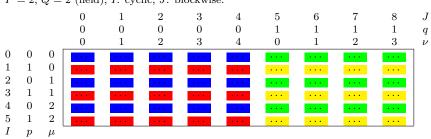

# Decomposition of Matrices I

With a matrix  $A \in \mathbb{R}^{N \times M}$  a real number  $a_{ij}$  is associated with each tupel  $(i, j) \in I \times J$ , with  $I = \{0, \dots, N-1\}$  and  $J = \{0, \dots, M-1\}$ .

To be able to represent the decomposed data on each processor again as a matrix, we limit the decomposition to the one-dimensional index sets I and J.

We assume processes are organised as a two-dimensional field:

$$(p,q) \in \{0,\ldots,P-1\} \times \{0,\ldots,Q-1\}.$$

The index sets I, J are decomposed to

$$I = \bigcup_{p=0}^{P-1} I_p$$

and  $J = \bigcup_{q=0}^{Q-1} J_q$

# **Decomposition of Matrices II**

Each process (p,q) is responsible for the indices  $I_p \times J_q$  and stores it's elements locally as  $\mathbb{R}(\tilde{I}_p \times \tilde{J}_q)$ -matrix.

Formally the decompositions of I and J are described as mappings p and  $\mu$  plus q and  $\nu$ :

$$\begin{split} I_p &= \{i \in I \mid p(i) = p\}, \quad \ \tilde{I}_p = \{n \in \mathbb{N} \mid \exists i \in I : p(i) = p \land \mu(i) = n\} \\ J_q &= \{j \in J \mid q(j) = q\}, \quad \ \tilde{J}_q = \{m \in \mathbb{N} \mid \exists j \in J : q(j) = q \land \nu(j) = m\} \end{split}$$

# Decomposition of a $6 \times 9$ Matrix to 4 Processors

# **Optimal Decomposition**

There is no overall best solution for the decomposition of matrices and vectors!

• In general a good load balancing is achieved if the subsets of the matrix are more or less quadratic.

- A good coordination with the algorithm used is usually more important. For example cyclic decomposition is a good solution for *LU*-decomposition, but not for the solution of the resulting triangular systems.

- Furthermore linear algebra is rarely a goal in it's own, but used in a more general context, like the solution of partial differential equations. The decomposition is then often given by the discretisation and the algorithm has to be flexible enough to deal with it.

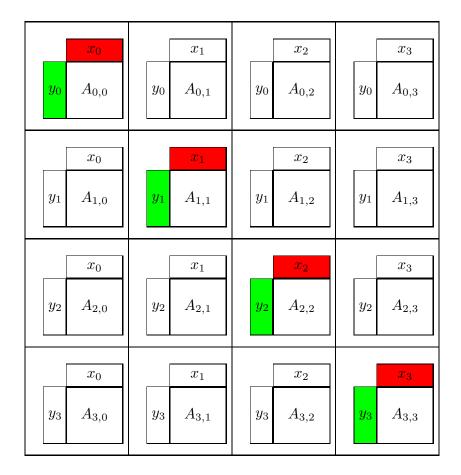

### 4.6 Matrix-Vector Multiplication

# Matrix-Vector Multiplication (fully-occupied matrix)

Aim: Calculate the product y = Ax of a matrix  $A \in \mathbb{R}^{N \times M}$  and a vector  $x \in \mathbb{R}^M$ .

Example: Matrix A distributed blockwise in a field, input vector x also blockwise as well as the result vector y.

The vector segment  $x_q$  is needed in each processor column.

Then each processor can calculate the local product  $y_{p,q} = A_{p,q}x_q$ .

Finally the complete result  $y_p = \sum_q y_{p,q}$  is collected in the diagonal processor (p,p) with an all-to-one communication.

### Matrix-Vector Multiplication: Parallel Runtime

Parallel runtime for a  $N \times N$ -matrix and  $\sqrt{P} \times \sqrt{P}$  processors with a cut-through communication network:

$$T_{P}(N,P) = \underbrace{\left(t_{s} + t_{h} + t_{w} \frac{N}{\sqrt{P}}\right) \operatorname{ld} \sqrt{P} + \underbrace{\left(\frac{N}{\sqrt{P}}\right)^{2} 2t_{f}}_{\text{Distribution of } x \text{ to column}}^{\text{Distribution of } x \text{ to column}}_{x \text{ to column}} + \underbrace{\left(t_{s} + t_{h} + t_{w} \frac{N}{\sqrt{P}}\right) \operatorname{ld} \sqrt{P}}_{\text{reduction}} = \operatorname{ld} \sqrt{P}(t_{s} + t_{h}) 2 + \frac{N}{\sqrt{P}} \operatorname{ld} \sqrt{P} 2t_{w} + \frac{N^{2}}{P} 2t_{f}$$

The contribution of the communication gets arbitrarily small if P and  $N \to \infty$ .

## 4.6.1 Things to Remember

# What you should remember

- The design of a parallel algorithm starts with decomposition of the task into parts which can be executed in parallel.

- Agglomerations is used to reduce the granularity and thus the communication overhead.

- Data decomposition is often important but can be done in different ways.

- There is no best solution for the decomposition of matrices and vectors. A good coordination with the algorithm is necessary.

## 5 Introduction Message Passing

### Message Passing

- Developed in the 60s

- Aim: Better structuring of parallel programs (networks didn't exist yet)

- Idea: Data which is needed by other processors is send as messages over the network

- Various powerful solutions available. Differences in elegance.

Examples:

- PVM (Parallel Virtual Machine) developed since 1989

- MPI (Message Parsing Interface) developed since 1994

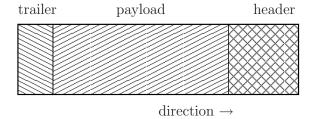

# Message Passing I

- Users view: Copy (contiguous) memory block from one address space to the other.

- Message is subdivided into individual packets.

- Network is packet-switched.

- A packet consists of an envelope and the data:

- Header: Destination, size and kind of data.

- Payload: Size ranges from some bytes to kilobytes.

- Trailer: E.g. checksum for error detection.

# Message Passing II

- Communication protocol: Flow-control, error detection and correction.

- $\bullet$  Time to send n bytes can be modelled as

$$t_{mess}(n) = t_s + n * t_b,$$

$t_s$ : latency,  $t_b$ : time per byte,  $t_b^{-1}$ : bandwidth.

- Latency is mostly software overhead, not hardware, and depends on the communication protocol.

- TCP/IP is an expensive wide-area network protocol with  $t_s \approx 100 \mu s$  (in Linux).

- Specialised networks with low-overhead protocols have  $t_s \approx 3 \dots 5 \mu s$ .

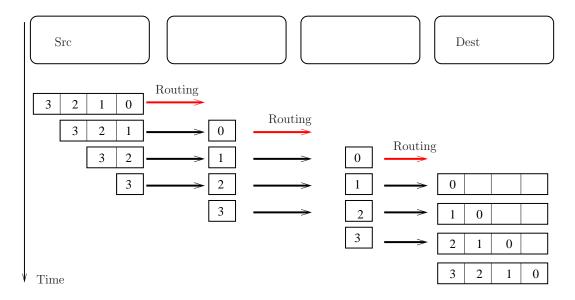

# **Cut-through Routing**

- Pipelining on word level.

- Time to send n bytes:  $t_{CT}(n, N, d) = t_s + t_h d + t_b n$ .

- Time is essentially independent of distance since  $t_h \ll t_s$ .

## 5.1 Synchronous Communication

### Send/Receive

The instructions for synchronous point-to-point communication are:

- $\operatorname{send}(\operatorname{dest} \operatorname{process}, \operatorname{expr}_1, \dots, \operatorname{expr}_n)$  Sends a message to the process  $\operatorname{dest} \operatorname{process}$  containing the expressions  $\operatorname{expr}_1$  to  $\operatorname{expr}_n$ .

- $\mathbf{recv}(src-process, var_1, \ldots, var_n)$  Receives a message from the process src-process and stores the results of the expressions in the variables  $var_1$  to  $var_n$ . The variables have to be of maching type.

### **Blocking**

Both **send** and **recv** are blocking, i.e. they are only finished, after the end of the communication. This synchronises the involved processes. Both sending and receiving process have to execute a matching pair of **send** and **recv** to avoid a deadlock.

#### Guards

Blocking communication is not sufficient for all possible tasks.

Sometimes a process does not know which of several partner processes is ready for data exchange.

Possible Solution: Non-blocking functions for detection if a partner process is ready for data reception or sending:

• int sprobe(dest - process)

Figure 1: (a) Synchronisation of two processes by a **send/recv** pair. (b) Example of a deadlock.

• int rprobe(src - process).

**sprobe** returns 1 (*true*), if the specified process is ready for a **recv**-operation, i.e. a **send**-command would *not* block the sender.

**rprobe** tests, if a **recv**-command would lead to a blockade. To avoid blocking of processes a communication instruction would be written as

• if  $(\operatorname{sprobe}(\Pi_d))$  send $(\Pi_d, \dots)$ ;

The instructions **sprobe** and **rprobe** are also called "guards".

# Implementation of rprobe and sprobe

Implementation of **rprobe** is easy. A **send**-instruction sends a message (or a part of it) to the receiver, where it is stored. The receiving process only needs to look up locally if a corresponding message (or part of it) has arrived.

Implementation of **sprobe** is more complicated, as usually the receiving process does not return any information to the sender. As one of the two instructions **sprobe/rprobe** is sufficient (at least in principle) only **rprobe** is used in practise.

# Receive Any

•  $recv_any(who, var_1, \dots, var_n)$

similar effect as **rprobe**allows reception of a message from any process

sender is stored in the variable *who*

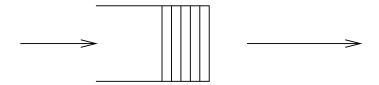

# 5.2 Asynchronous Communication

### **Asynchronous Communication**

- $asend(dest process, expr_1, \dots, expr_n)$

- $arecv(src process, var_1, \dots, var_n)$

have the same semantic as **send/recv**, but are *non-blocking*.

In principle a process can execute any amount of **asend** instructions without delay.

The involved processes are *not* synchronised implicitly.

Beginning and end of the communication channel can be visualised as a waiting line, buffering all messages until they are accepted by the receiving process.

### **Check for Success**

In practise buffer storage is limited. If the buffer is full, no further **asend** instruction can be executed. Therefore it is necessary to test if a former communication instruction has been completed.

asend/arecv are returning a unique identifier

- msgid asend(...)

- msgid arecv(...)

With this identifier the function

• int success(msgid m)

returns the state of the communication.

### Mixing of Synchronous and Asynchronous Communication

We are going to allow mixing of the functions for asynchronous and synchronous communication. For example the combination of asynchronous sending and synchronous receiving can make sense.

### 6 Debugging of Parallel Programs

Debugging parallel programs is a complicate task. Possible tools are:

- Using printf or std::cout

- Writting to log files

- Using gdb

- Using specialised debuggers for parallel programs

## Using printf or std::cout

```

std::cout << omp_get_thread_num() << ":||a||=||" << a << std::endl;

```

- Output should be prefixed with the rank (number) of the process

- Output of different processes is mixed and written by the root process.

- The order of output from different processes must not be chronological

- If job terminates some output may never be written

## Writing to log-files

```

template < class T>

void DebugOut(const std::string message, T i) const

{

std::ostringstream buffer;

buffer << "debugout" << myRank_;

std::ofstream outfile(buffer.str().c_str(),std::ios::app);

outfile << message << "" << i<< std::endl;

}</pre>

```

- Output from each processor goes to a separate file

- Output is complete for each processor (as file is always immediately closed afterwards)

- File is allways appended not erased  $\Rightarrow$  output of several runs can be mixed

### Using gdb (with Message Passing)

To make sure that all processes are still at the beginning you can add an infinite loop

```

1 bool debugStop=true;

while (debugStop);

```

After gdb has attached the loop can be exited by using the gdb-command

```

set debugStop=true;

```

You may have to compile with

```

1 mpicxx -o <program name> -g -00 <program source>

```

as the compiler may optimise the variable away if the option -00 is absent.

# **Parallel Debuggers**

- Parallel debuggers are providing a graphical user interface for the process describe before

- Commercial parallel debuggers are e.g. Totalview and DDT

- There is also a eclipse plugin available: PTP

# 7 The Message Passing Interface

# The Message Passing Interface (MPI)

- Portable Library with functions for message exchange between processes

- Developed 1993-94 by a international board

- Available on nearly all computer platforms

- Free Implementations also for LINUX Clusters: MPICH<sup>1</sup> and OpenMPI<sup>2</sup> (former LAM)

- Properties of MPI:

- library with C-, C++ and Fortran bindings (no language extension)

- large variety of point-to-point communication functions

- global communication

- data conversion for heterogeneous systems

- subset formation and topologies possible

MPI-1 consits of more than 125 functions, defined in the standard on 200 pages. We therefore only treat a small selection of it's functionality.

## 7.1 Simple Example

# Simple Example in C

```

#include <stdio.h>

2 #include <string.h>

#include <mpi.h> // provides MPI macros and functions

6 int main (int argc, char *argv[])

{

int my_rank;

int P;

int dest;

10

int source;

int tag=50;

12

char message[100];

MPI_Status status;

14

MPI_Init(&argc,&argv); // begin of every MPI program

MPI_Comm_size(MPI_COMM_WORLD,&P); // number of

18

// involved processes

MPI_Comm_rank(MPI_COMM_WORLD,&my_rank);

20

// number of current process always between 0 and P-1

sprintf(message,"I_am_process_%d_of_%d\n",my_rank,P);

22

if (my_rank!=0)

dest = 0;

MPI_Send(message,strlen(message)+1,MPI_CHAR, // Send data

26

dest,tag,MPI_COMM_WORLD);

// (blocking)

```

$<sup>^{1}{\</sup>rm http://www-unix.mcs.anl.gov/mpi/mpich}$

$<sup>^2</sup>$ http://www.open-mpi.org/

```

}

28

else

30

puts(message);

for (source=1; source<P; source++)</pre>

32

MPI_Recv(message,100,MPI_CHAR,source,tag, // Receive data

34

// (blocking)

MPI_COMM_WORLD,&status);

puts(message);

}

}

MPI_Finalize(); // end of every MPI program

40

return 0;

42

```

## Simple Example in C++

```

1 #include <iostream>

#include <sstream>

3 #include <mpi.h> // provides MPI macros and functions

int main (int argc, char *argv[])

7 {

MPI::Init(argc,argv); // begin of every MPI program

9

int P = MPI::COMM_WORLD.Get_size(); // number of

// involved processes

11

int myRank = MPI::COMM_WORLD.Get_rank();

13

int tag=50;

// number of current process always between 0 and P-1 \,

15

if (myRank != 0)

17

std::ostringstream message;

message << "Iuamuprocessu" << myRank << "uofu" << P << std::endl;

19

int dest = 0;

// Send data

21

MPI::COMM_WORLD.Send(message.str().c_str(),

message.str().size()+1,MPI::CHAR,dest,tag); // (blocking)

}

23

else

24

std::cout << "Iuamuprocessu0uofu" << P << std::endl << std::endl;

for (int source=1; source <P; ++source)</pre>

28

char message[100];

MPI::COMM_WORLD.Recv(message,100,MPI_CHAR, // Receive data

30

source,tag);

// (blocking)

std::cout << message << std::endl;</pre>

32

}

MPI::Finalize(); // end of every MPI program

36

return 0;

38

```

# **Compilation of Program**

- Sample program is written in SPMD-Stile. This is not prescribed by the MPI Standard, but makes starting of program easier.

- Compiling, linking and execution is different for every implementation.

- Many implementations contain shell-scripts, which hide the location of the libraries. For MPICH the commands to compile the program and start 8 processes are

```

mpicc -o hello hello.c

mpirun -machinefile machines -np 8 hello

```

In this case the names of the computers used are taken from the file machines.

For C++ programs the command for compilation is

```

mpicxx -o hello hello.c

```

# Output of the Example Programs (with P=8)

```

1

I

am

process

0

of

8

3

I

am

process

1

of

8

5

I

am

process

2

of

8

7

I

am

process

3

of

8

9

I

am

process

4

of

8

11

I

am

process

5

of

8

13

I

am

process

6

of

8

15

I

am

process

7

of

8

```

### Structure of MPI-Messages

MPI-Messages consist of the actual data and an envelope comprising:

- 1. number of the sender

- 2. number of the receiver

- 3. tag: an integer value to mark different messages between identical communication partners

- 4. communicator: subset of processes + communication context. Messages belonging to different contexts don't influence each other. Sender and receiver have to use the same communicator. The communicator MPI\_COMM\_WORLD is predefined by MPI and contains all started processes.

In C++ communicators are objects over which the messages are sent. The communicator object  $\mathtt{MPI}::\mathtt{COMM\_WORLD}$  is already predefined.

# **Initialising and Finishing**

```

int MPI_Init(int *argc, char ***argv)

void Init(int& argc, char**& argv)

void Init()

Before the first MPI functions are used, MPI_Init / MPI::Init has to be called.

int MPI_Finalize(void)

void Finalize()

```

After the last MPI function call MPI\_Finalize / MPI::Finalize must be executed to get a defined shutdown of all processes.

# 7.2 Communicators and Topologies

### Communicator

All MPI communication functions contain an argument of type MPI\_Comm (in C) or are methods of a communicator object. Such a *communicator* contains the following abstractions:

- Process group: builds a subset of processes which take part in a global communication. The predefined communicator MPI\_COMM\_WORLD contains all started processes.

- Context: Each communicator defines it's own communication context. Messages can only be received within the same context in which they are send. It's e.g. possible for a numerical library to define it's own communicator. The messages of the library are then completely separated from the messages of the main program.

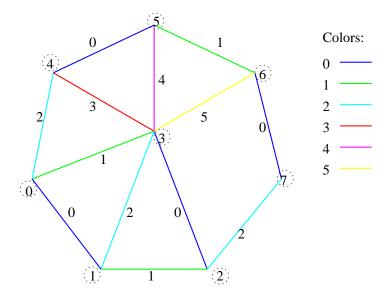

- Virtual Topologies: A communicator represents a set of processes  $\{0, \ldots, P-1\}$ . This set can optionally be provided with an additional structure, e.g. a multi-dimensional field or a general graph.

- Additional Attributes: An application (e.g. a library) can associate any static data with a communicator. The communicator is then only a means to preserve this data until the next call of the library.

# Communicators in C++

In C++ communicators are objects of classes derived from a base class  ${\tt Comm}$ . The available derived classes are

Intracomm for the communication inside a group of processes. MPI::COMM\_WORLD is an object of class Intracomm as all processes are included in MPI::COMM\_WORLD. There exist two derived classes for the formation of topologies of processes

Cartcomm can represent processes which are arranged on a Cartesian topology Graphcomm can represent processes which are arranged along arbitrary graphs

Intercomm for the communication between groups of processes

### **Determining Rank and Size**

```

int MPI_Comm_size(MPI_Comm comm, int *size)

2

int Comm::Get_size() const

```

The number of processes in a communicator is determined by the function MPI\_Comm\_size / Comm::Get\_size(). If the communicator is MPI\_COMM\_WORLD this is equal to the total number of started processes.

```

int MPI_Comm_rank(MPI_Comm comm, int *rank)

2

int Comm::Get_rank() const

```

Each process has a unique number inside a group represented by a communicator. This number can be determined by MPI\_Comm\_rank / Comm::Get\_rank().

# 7.3 Blocking Communication

The first three arguments message, count, and dt, specify the actual data. message points to a contiguous memory block containing count elements of type dt. The specification of the data type makes data conversion by MPI possible. The arguments dest, tag and comm form the envelope of the message (the number of the sender/receiver is given implicitly by the invocation).

#### **Data Conversion**

MPI implementations for heterogeneous systems are able to do a automatic conversion of the data representation. The conversion method is left to the particular implementation (e.g. by XDR).

MPI provides the architecture independent data types:

MPI\_CHAR, MPI\_UNSIGNED\_CHAR, MPI\_BYTE MPI\_SHORT, MPI\_INT, MPI\_LONG, MPI\_LONG\_LONG\_INT, MPI\_UNSIGNED, MPI\_UNSIGNED\_SHORT, MPI\_UNSIGNED\_LONG, MPI\_FLOAT, MPI\_DOUBLE and MPI\_LONG\_DOUBLE.

IN C++ the datatypes are:

MPI::CHAR, MPI::UNSIGNED\_CHAR, MPI::BYTE MPI::SHORT, MPI::INT, MPI::LONG, MPI::LONG\_LONG\_INT, MPI::UNSIGNED, MPI::UNSIGNED\_SHORT, MPI::UNSIGNED\_LONG, MPI::FLOAT, MPI::DOUBLE and MPI::LONG\_DOUBLE.

The MPI data type MPI\_BYTE / MPI::BYTE is never converted.

#### **Status**

```

typedef struct {

2    int count;

int MPI_SOURCE;

4    int MPI_TAG;

int MPI_ERROR;

6 } MPI_Status;

```

In C MPI\_Status is a struct containing information about the number of received objects, source rank, tag and an error status.

```

int Status::Get_source() const

void Status::Set_source(int source)

int Status::Get_tag() const

void Status::Set_tag(int tag)

int Status::Get_error() const

void Status::Set_error(int error)

```

In C++ an object of class Status provides methods to access the same information.

### Varieties of Send

- buffered send (MPI\_Bsend / Comm::Bsend): If the receiver has not yet executed a corresponding recv-function, the message is buffered by the sender. If enough memory is available, a "buffered send" is always terminated immediately. In contrast to asynchronous communication the sending buffer message can be immediately reused.

- synchronous send (MPI\_Ssend / Comm::Ssend): The termination of a synchronous send indicates, that the receiver has executed the recv-function and has started to read the data.

- ready send (MPI\_Rsend / Comm::Rsend): A ready send can only be started if the receiver has already executed the corresponding recv. The call leads to an error else.

### MPI\_Send and MPI\_Receive | |

The MPI\_Send-command either has the semantic of MPI\_Bsend or MPI\_Ssend, depending on the implementation. Therefore MPI\_Send can, but don't have to block. The sending buffer can be reused immediately in any case.

The function MPI\_Recv is in any case blocking, e.g. it is only terminated if message contains data. The argument status contains source, tag and error status of the received message.

MPI\_ANY\_SOURCE / MPI::ANY\_SOURCE and MPI\_ANY\_TAG / MPI::ANY\_TAG can be used for the arguments src and tag respectively. Thus MPI\_Recv contains the functionality of recv\_any.

### **Guard Function**

is a non-blocking guard function for the receiving of messages. flag is set to true true  $(\neq 0)$  if a message with matching source and tag can be received. The arguments MPI\_ANY\_SOURCE / MPI::ANY\_SOURCE and MPI\_ANY\_TAG / MPI::ANY\_TAG are also possible.

### 7.4 Non-blocking communication

MPI provides the functions

for non-blocking communication. They imitate the respective communication operations. With the MPI\_Request / MPI::Request-objects the state of the communication job can be checked (corresponding to our msgid).

## MPI\_Request-Objects

The state of the communication can be checked with MPI\_Request-objects returned by the communication functions using the function (among others)

```

int MPI_Test(MPI_Request *req,int *flag, MPI_Status *status);

```

flag is set to true  $(\neq 0)$  if the communication job designated by req has terminated. In this case status contains information about sender, receiver and error state.

```

bool Request::Test(Status& status)

bool Request::Test()

```

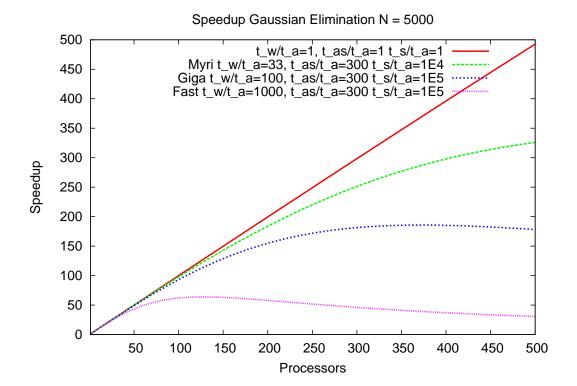

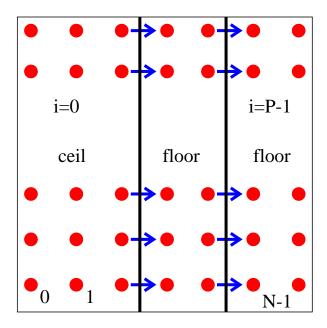

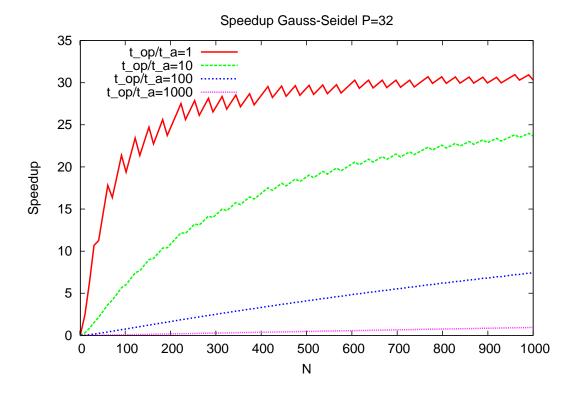

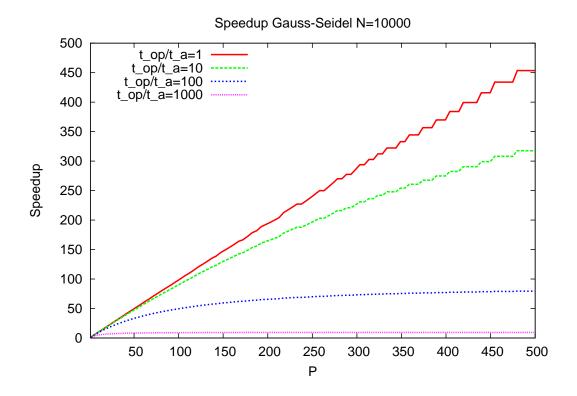

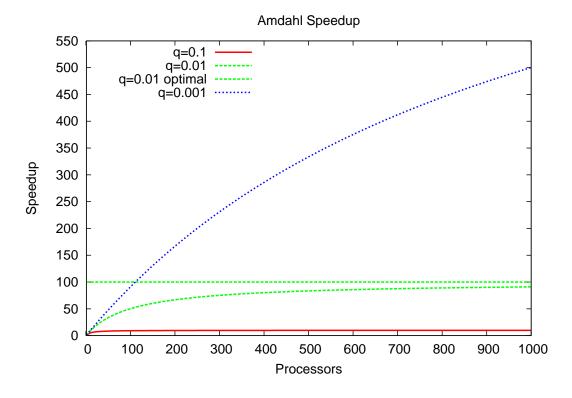

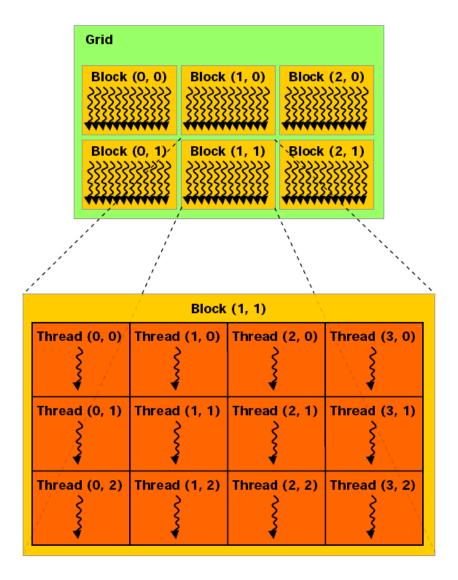

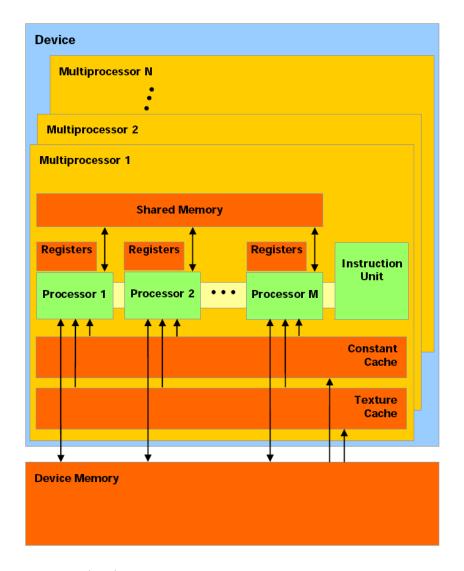

In C++ the Test method of the Request object returned by the communicator method returns true if the job initiated by the method call has terminated.